# Scalable Interconnect Strategies for Neuro-glia Networks using Networks-on-Chip

# **George Stephen Martin (BEng)**

Faculty of Computing, Engineering and the Built Environment

A thesis submitted for the degree of Doctor of Philosophy (PhD)

August 2018

"I confirm that the word count of thesis is less than 100,000 words"

# **Abstract**

Hardware has become more prone to faults, due to wear-out and faults caused during the manufacturing process. The reliability of hardware is becoming more dependent on the ability to continually adapt to faults and current fault tolerant approaches are susceptible to faults. A computational model of biological self-repair in the brain, derived from observing the distributed role of astrocytes (a glial cell found in the mammalian brain), has captured self-repair within neural networks; these are known as neuro-glia networks.

Astrocytes have been shown to facilitate biological self-repair in silent or near silent neurons in the brain by increasing the Probability of Release (PR) in healthy synapses. Astrocytes modulate synaptic activity, which leads to increased or decreased PR. To date, this has been proven with computational modelling and therefore, the next step is to replicate this self-repair process in hardware to provide self-repairing electronic information processing systems. A key challenge for hardware neuro-glia networks implementation is the facilitation of scalable communication between interacting neurons and astrocyte cells. There are large volumes of neurons/ astrocytes with different communication patterns and this network is viewed as a two-tiered network:

- 1. High speed temporal spike event (neural network)

- 2. Low speed numerical inositol trisphosphate information exchange (astrocyte network).

This thesis addresses the key challenge of providing scalable communication for a neuro-glia network with low-level Networks-on-Chip (NoC) topologies. This network supports astrocyte to neuron/synapse communication at a local level and astrocyte communication at a global level i.e. the astrocyte network. The astrocyte process is inherently slow, thus a ring topology exploits this slow change and sacrifices high throughput for a low area overhead, this is analogous to the astrocyte process. This astrocyte was applied in hardware and results demonstrate that novel ring topology provides a trade-off between low area/interconnect wiring overhead whilst supporting realistic communication speeds for both the slow-changing data between astrocytes and the higher throughput neuron networks.

#### NOTE ON ACCESS TO CONTENTS

I hereby declare that with effect from the date on which the thesis is deposited in Research Office of the Ulster University, I permit

- 1. The Librarian of the University to allow the thesis to be copied in whole or in part without reference to me on the understanding that such authority applies to the provision of single copies made for study purposes or for inclusion within the stock of another library.

- 2. The thesis to be made available through the Ulster Institutional Repository and/or EThOS under the terms of the Ulster eTheses Deposit Agreement which I have signed.

IT IS A CONDITION OF USE OF THIS THESIS THAT ANYONE WHO CONSULTS IT MUST RECOGNISE THAT THE COPYRIGHT RESTS WITH THE AUTHOR AND THAT NO QUOTATION FROM THE THESIS AND NO INFORMATION DERIVED FROM IT MAY BE PUBLISHED UNLESS THE SOURCE IS PROPERLY ACKNOWLEDGED.

(George Martin)

# **Table of Contents**

| List of Figures                                          | vii  |

|----------------------------------------------------------|------|

| List of Tables                                           | x    |

| Abbreviations                                            | xi   |

| Acknowledgements                                         | xiii |

| Dedication                                               | xiv  |

| Chapter 1: Introduction                                  | 1    |

| 1.1 Background                                           | 1    |

| 1.2 Thesis Contributions                                 | 5    |

| 1.3 Thesis Outline                                       | 6    |

| 1.4 Publications                                         | 8    |

| 1.4.1 Conference papers                                  | 8    |

| 1.4.2 Journal Papers                                     | 8    |

| 1.5 Summary of contributions                             | 9    |

| Chapter 2: From biology to hardware                      | 13   |

| 2.1 Introduction                                         | 13   |

| 2.2 Neural information processing                        | 14   |

| 2.2.1 Neurons                                            | 15   |

| 2.3 Neural networks                                      | 17   |

| 2.3.1 Spiking neural networks                            | 19   |

| 2.4 Neural networks: computational implementations       | 22   |

| 2.4.1 Neural networks in software                        | 22   |

| 2.4.2 Neural networks in firmware                        | 25   |

| 2.4.3 Neural networks in ICs                             | 26   |

| 2.4.4 Neural network hardware using on-chip interconnect | 28   |

| 2.5 Astrocytes and self-repair                           | 31   |

| 2.5.1 Example computational models of repair             |      |

| 2.6 Astrocytes in hardware                               |      |

| 2.7 Challenges                                           |      |

| 2.8 Summary                                              |      |

| Chapter 3: Networks-on-Chip: an innovative solution                                 | 42 |

|-------------------------------------------------------------------------------------|----|

| 3.1 Introduction                                                                    | 42 |

| 3.2 NoC interconnect advantages                                                     | 45 |

| 3.3 NoC components                                                                  | 50 |

| 3.3.1 NoC topologies                                                                | 50 |

| 3.3.2 Traditional topologies                                                        | 51 |

| 3.3 Advanced hierarchical topology                                                  | 55 |

| 3.4 NoC communication                                                               | 56 |

| 3.4.1 Routing algorithm                                                             | 58 |

| 3.4.2 Router micro-architecture                                                     | 59 |

| 3.5 Challenges of a neuro-glia NoC interconnect                                     | 61 |

| 3.6 Summary                                                                         | 63 |

| Chapter 4: The Fault Model                                                          | 65 |

| 4.1 Background                                                                      | 65 |

| 4.2 Fault tolerance and self-repair strategies                                      | 66 |

| 4.2.1 Online testing                                                                | 68 |

| 4.2.2 Hardware redundancy                                                           | 69 |

| 4.2.3 Autonomous self-repair                                                        | 69 |

| 4.3 Fault models                                                                    | 70 |

| 4.4 Drawbacks of existing approaches                                                | 73 |

| 4.5 The Objective                                                                   | 74 |

| 4.6 Summary                                                                         | 76 |

| Chapter 5: Local communication: Astrocyte to neuron communication using a ring NoC. | 77 |

| 5.1 Introduction                                                                    | 77 |

| 5.2 Network design challenges and constraints                                       | 79 |

| 5.3 Neuro-glia network repair                                                       | 80 |

| 5.4 Low-level neuro-glia interconnect                                               | 83 |

| 5.4.1 The astrocyte process in hardware                                             | 85 |

| 5.4.2 Packetisation of the e-SP signal                                              | 88 |

| 5.4.3 The e-SP signal                                                               | 91 |

| 5.5 Results                                                                         | 92 |

| 5.6 Summary                                                                       | 99  |

|-----------------------------------------------------------------------------------|-----|

| Chapter 6: On-chip communication for neuro-glia networks: Global NoC              | 101 |

| 6.1 Introduction                                                                  | 101 |

| 6.2 Neuro-glia networks: Biology                                                  | 103 |

| 6.2.1 Neurons and glia cells                                                      | 103 |

| 6.2.2 How the brain facilitates self-repair                                       | 105 |

| 6.2.3 NoC for neuro-glia network                                                  | 106 |

| 6.3 Astrocyte tile router overview                                                | 106 |

| 6.3.1 Global communication in a neuro-glia network                                | 107 |

| 6.3.2 Astrocyte tile: Inter-router module and topology                            | 109 |

| 6.3.3 Update manager and dynamic scheduler                                        | 112 |

| 6.4 Results and analysis                                                          | 115 |

| 6.4.1 Performance: Astrocyte tile router                                          | 116 |

| 6.4.2 Scalability analysis                                                        | 117 |

| 6.4.3 Power analysis with dynamic scheduler                                       | 119 |

| 6.5 Conclusion                                                                    | 122 |

| Chapter 7: Application of spiking astrocyte-neuron network using Networks-on-Chip | 125 |

| 7.1 Introduction                                                                  | 125 |

| 7.2 The spiking astrocyte-neuron network                                          | 126 |

| 7.2.1 An overview of the robotic car architecture                                 | 126 |

| 7.2.2 The astrocyte process                                                       | 129 |

| 7.3 e-SP and the astrocyte neuron network                                         | 131 |

| 7.4 Self-repair using "e-SP comms" ring                                           | 134 |

| 7.5 Fault Scenarios                                                               | 139 |

| 7.6 Summary                                                                       | 140 |

| Chapter 8: Conclusion and future work                                             | 142 |

| 8.1 Conclusion                                                                    | 142 |

| 8.2 Thesis Contributions                                                          | 146 |

| 8.3 Future Work                                                                   | 147 |

| hliography                                                                        | 152 |

# **List of Figures**

| Fig.2.1 A neuron by Ramon y Cajal                                            | 15 |

|------------------------------------------------------------------------------|----|

| Fig.2.2 Synaptic cleft                                                       | 15 |

| Fig.2.3 A closer look at the neuron                                          | 16 |

| Fig.2.4 An action potential/spike                                            | 17 |

| Fig.2.5 Simplified overview of an ANN                                        | 18 |

| Fig.2.6 Hodgkin and Huxley model                                             | 20 |

| Fig.2.7 Biological plausibility vs computational complexity                  | 22 |

| Fig.2.8 IBM infographic on TrueNorth                                         | 27 |

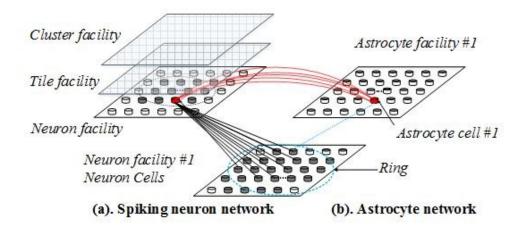

| Fig.2.9 H-NoC Architecture.                                                  | 30 |

| Fig.2.10 H-NoC/Astrocyte Architecture.                                       | 30 |

| Fig.2.11 Astrocyte feedback:                                                 | 32 |

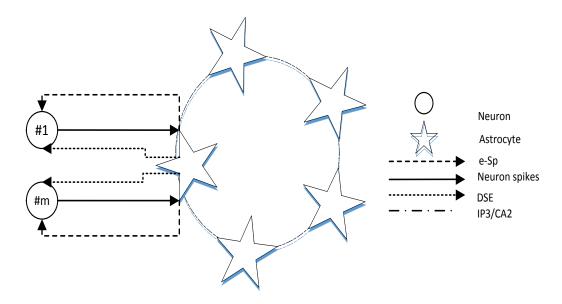

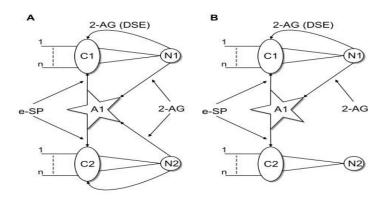

| Fig.2.12 SNN with Neurons and Astrocytes.                                    | 34 |

| Fig.2.13 SPANNER repair mechanism no fault                                   | 36 |

| Fig.2.14 SPANNER repair mechanism with faults                                | 37 |

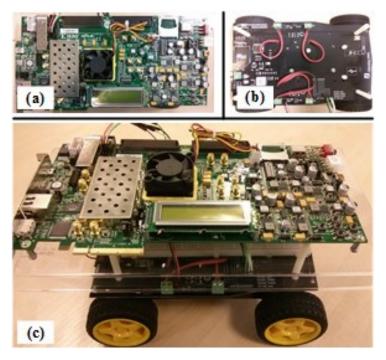

| Fig.2.15 Mobile Car controlled by an FPGA based SANN                         | 38 |

| Fig.3.1 A typical system bus                                                 | 42 |

| Fig.3.2 A typical mesh NoC infrastructure.                                   | 43 |

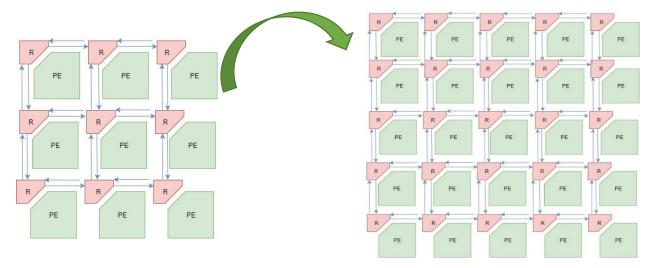

| Fig.3.3 Scaling NoCs, comparing a 3x3 array to a 5x5 array                   | 45 |

| Fig.3.4 A theoretical overview of astrocyte and neuron routers communicating | 47 |

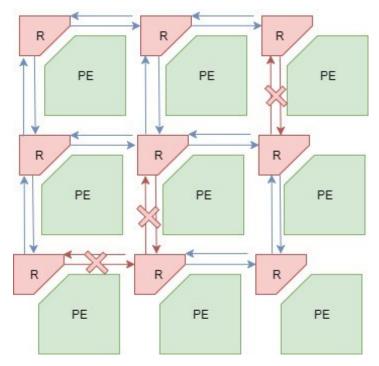

| Fig.3.5 Faults occurring in an NoC interconnect                              | 49 |

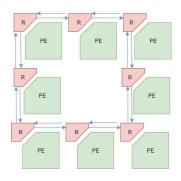

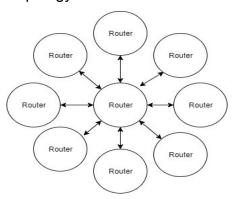

| Fig.3.6 Ring topology                                                        | 52 |

| Fig.3.7 Mesh topology                                                        | 52 |

| Fig.3.8 Torus topology                                                       | 52 |

| Fig.3.9 Star topology                                                        | 53 |

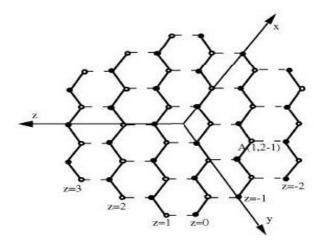

| Fig.3.10 Honeycomb topology                                                  | 54 |

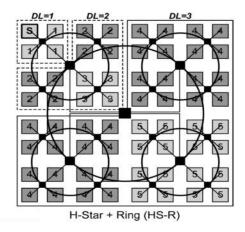

| Fig.3.11 Star ring topology                                                  | 56 |

| Fig.3.12 A Typical NoC packet                                                | 57 |

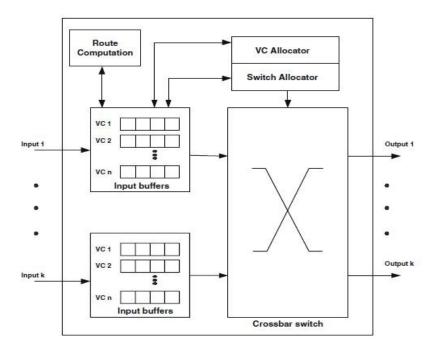

| Fig.3.13 NoC Router Micro-architecture                                       | 60 |

| Fig.4.1 A large scale neuro-glia network.                                    | 75 |

| Fig.5.1 Computational astrocyte model                                     | 81  |

|---------------------------------------------------------------------------|-----|

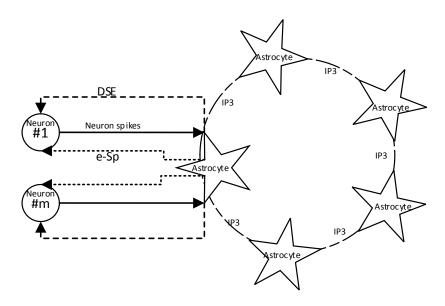

| Fig.5.2 Neuro-glia network outlining the major signals within the network | 84  |

| Fig.5.3 Neurons vs astrocyte communication.                               | 85  |

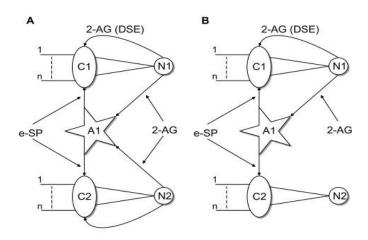

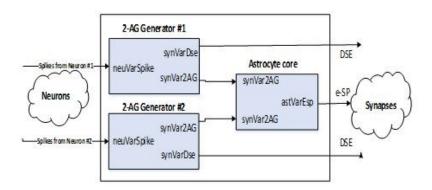

| Fig. 5.4 2-AG generator communicating to the Astrocyte producing e-SP     | 86  |

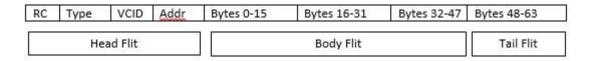

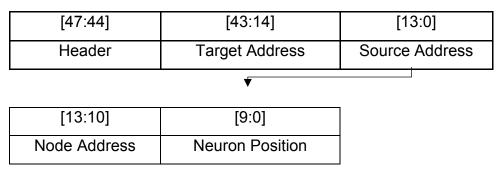

| Fig.5.5 H-NoC packet description                                          | 88  |

| Fig. 5.6 The e-SP packet in closer detail.                                | 89  |

| Fig.5.7 The e-SP Tx and Rx modules.                                       | 90  |

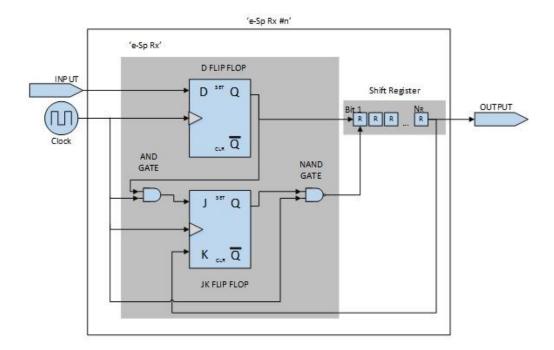

| Fig.5.8 The e-SP Rx module                                                | 91  |

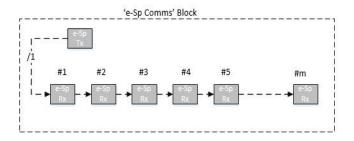

| Fig.5.9 "e-SP comms" module                                               | 93  |

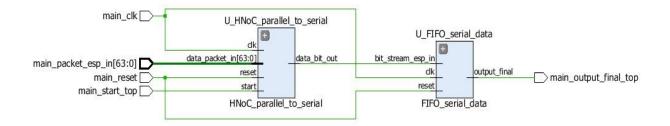

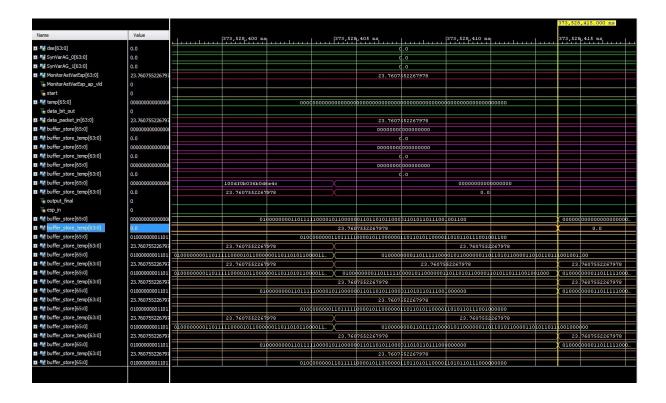

| Fig.5.10 "e-SP comms" module showing the simulation.                      | 94  |

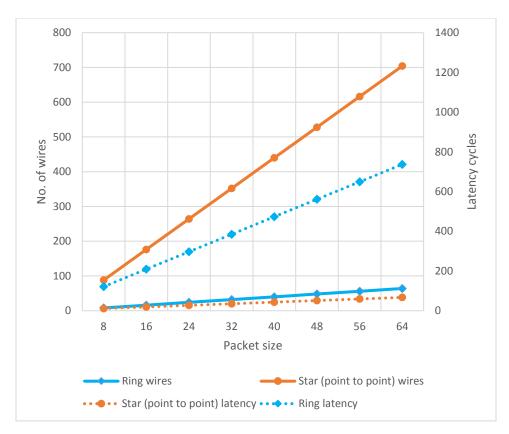

| Fig.5.11 e-SP comms module scalability.                                   | 96  |

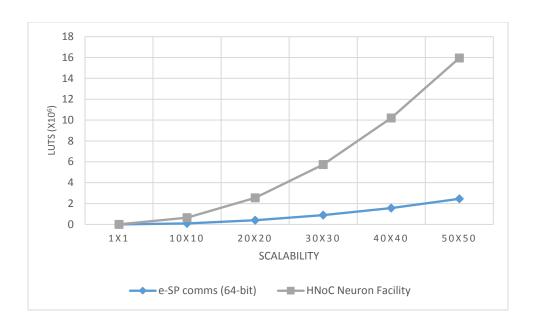

| Fig.5.12 e-SP comms module vs H-NoC neuron facility (scalability).        | 97  |

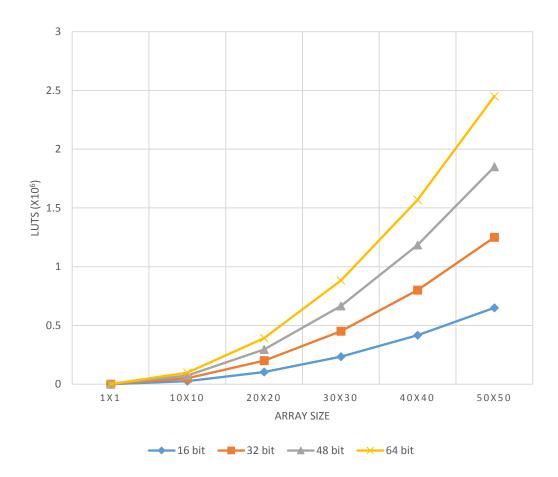

| Fig.5.13 Area utilisation scaling the e-SP comms module                   | 98  |

| Fig.6.1 Glia/neuron ratio                                                 | 104 |

| Fig.6.2 Communication signals within a neuro-glia network.                | 107 |

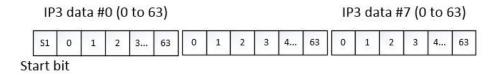

| Fig.6.3 Packet layout                                                     | 110 |

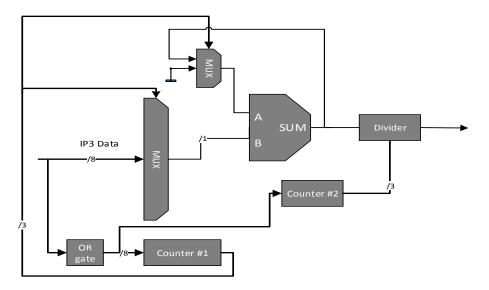

| Fig.6.4 IP <sub>3</sub> accumulator.                                      | 111 |

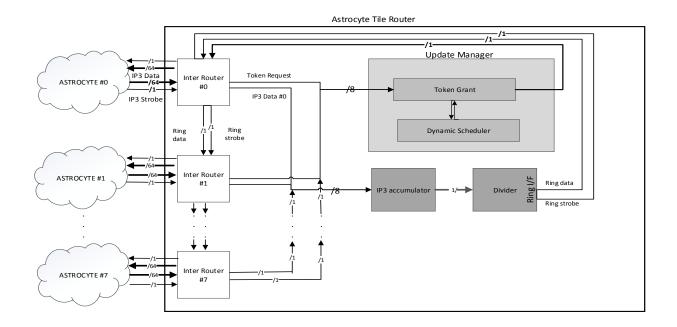

| Fig.6.5 Astrocyte tile router communications.                             | 112 |

| Fig.6.6 Update manager DS flow chart.                                     | 114 |

| Fig.6.7 Scalability LUTs and slice registers.                             | 118 |

| Fig.6.8 Dynamic scheduler evaluation.                                     | 120 |

| Fig.6.9 Scalability in terms of astrocyte tile routers.                   | 122 |

| Fig.7.1 Astrocyte feedback.                                               | 127 |

| Fig.7.2 The FPGA based robotic car                                        | 127 |

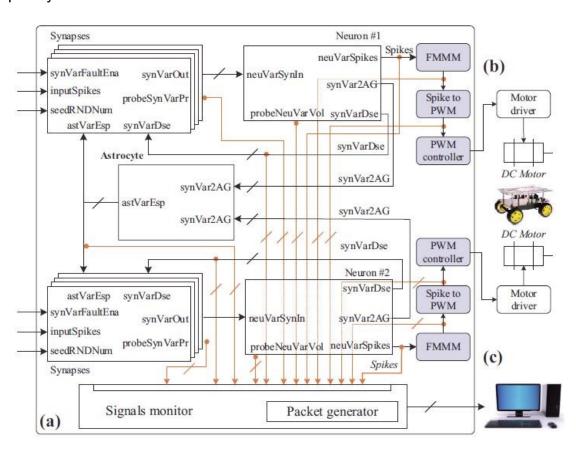

| Fig.7.3 Overview of the hardware architecture                             | 128 |

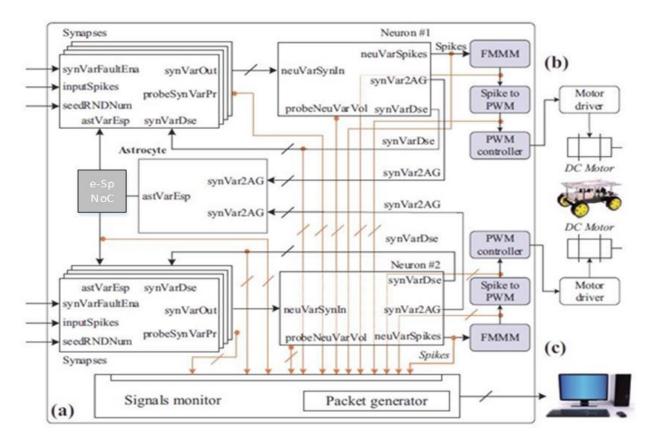

| Fig.7.4 Overview of the hardware architecture with e-SP ring NoC.         | 130 |

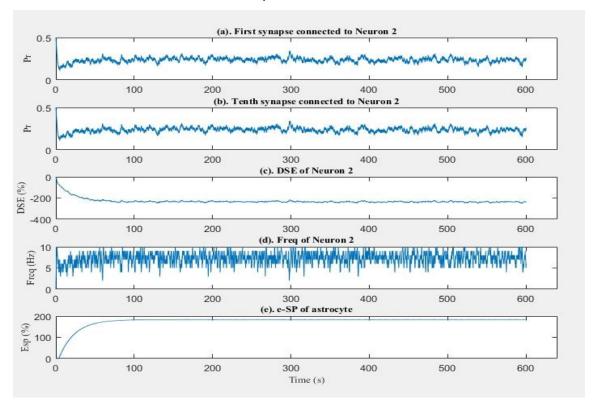

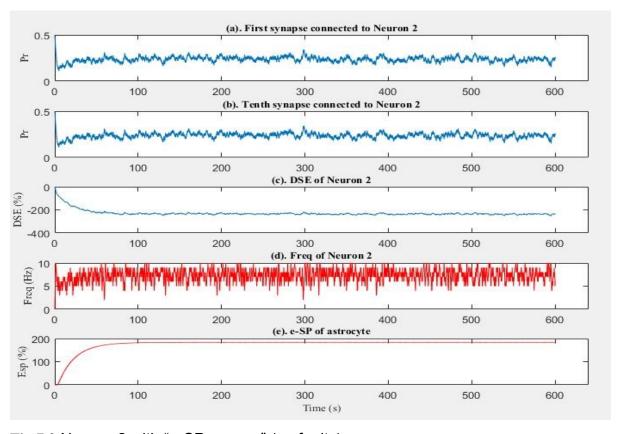

| Fig.7.5 Neuron 2 regular activity with no faulty synapses.                | 131 |

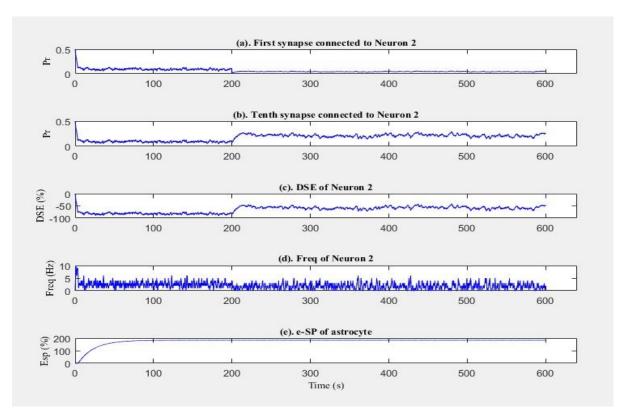

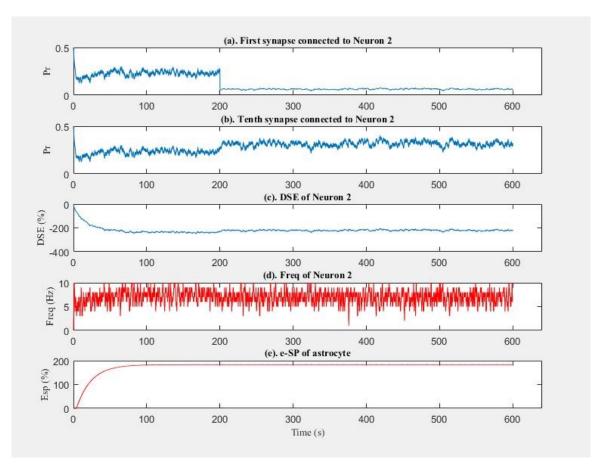

| Fig.7.6 Neuron 2 faults with no e-SP.                                     | 132 |

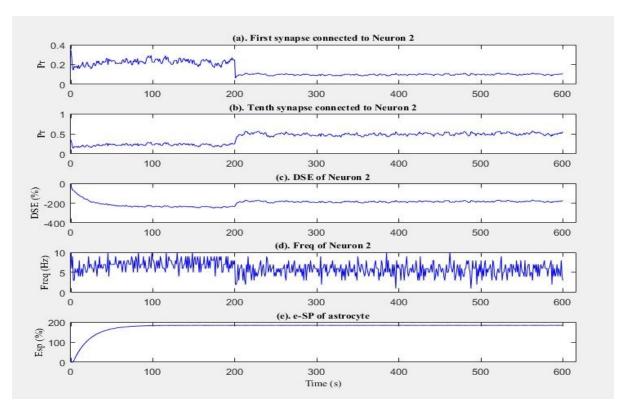

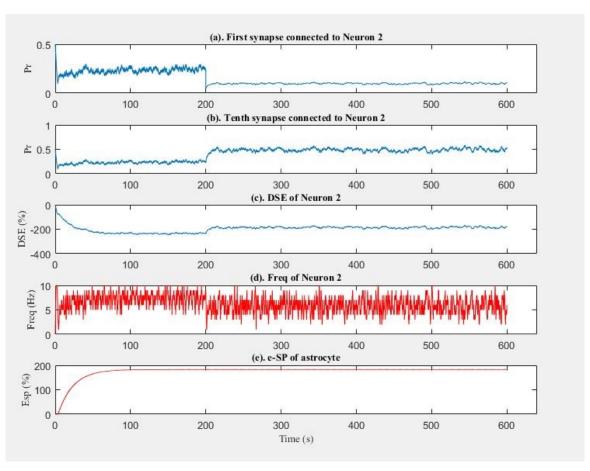

| Fig.7.7 Neuron 2 faults with e-SP.                                        | 133 |

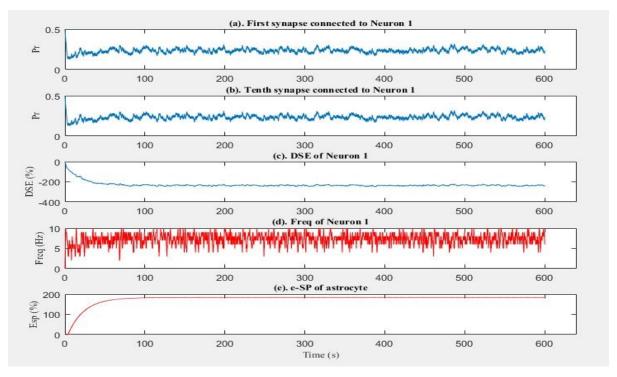

| Fig.7.8 Neuron 1 with "e-SP comms" (no faults).                           | 135 |

| Fig 7.9 Neuron 2 with "e-SP comms" (no faults)                            | 135 |

| Fig.7.10 Neuron 2 with "e-SP comms" | " (40% faults) | 136 |

|-------------------------------------|----------------|-----|

| Fig.7.11 Neuron 2 with "e-SP comms" | " (80% faults) | 137 |

# **List of Tables**

| Table 3.1 Comparing traditional network topologies                                 | 54  |

|------------------------------------------------------------------------------------|-----|

| Table 5.1 Astrocyte signals and values                                             | 81  |

| Table 5.2 Area analysis "e-SP comms"                                               | 95  |

| Table 6.1 Neurons to glia cells (based on region)                                  | 104 |

| Table 6.2 Neuron to glia ratios.                                                   | 105 |

| Table 6.3 'Astro-Router' block evaluation                                          | 116 |

| Table 6.4 Power analysis with varied t <sub>DS</sub>                               | 119 |

| Table 6.5 Power analysis                                                           | 120 |

| Table 6.6 Power Analysis of individual components within the astrocyte tile router | 121 |

| Table 6.7 Power analysis per component.                                            | 122 |

| Table 7.1 SANN area analysis                                                       | 133 |

| Table 7.2 e-SP ring relative area analysis                                         | 137 |

| Table 7.3 Average frequencies of different platforms                               | 138 |

| Table 7.4 Comparing average frequencies with and without the e-SP ring             | 138 |

#### **Abbreviations**

2-AG Glutamate

ANN Artificial Neural Network

AP Action Potential

ASIC Application Specific Integrated Chip

CA<sup>2+</sup> Calcium

CPU Central Processor Unit

CRC Cyclic Redundancy Check

DARPA Defence Advanced Research Projects Agency

DSE Depolarization-induced Suppression of Excitation

EMBRACE Emulating Biologically-Inspired Architecture in Hardware

e-SP Endocannabinoid-mediated Synaptic Potentiation

FIFO First In First Out

FPGA Field Programmable Gate Array

FSM Finite State Machine

GPU Graphic Processor Unit

HANA Hierarchical astrocyte network architecture

HICANN High Input Count Analog Neural Network

H-NoC Hierarchical Networks on Chip

HPC High-Performance Computer

IF Integrate and Fire

IP<sub>3</sub> Inositol trisphosphate

LIF Leaky Integrate and Fire

LUT Look Up Table

MLP Multilayer perceptron

MPSoC Multi-Processor System-on-Chip

NoC Networks-on-Chip

PE Processing Element

PISO Parallel In Serial Out

PR Probability of Release

PWM Pulse Width Modulator

SANN Spiking Astrocyte-Neuron Network

SLP Single Layer Perceptron

SNN Spiking Neural Network

SoC System-on-Chip

SRM Spike Response Model

SyNAPSE Systems of Neuromorphic Adaptive Plastic Scalable Electronics

TMR Triple Mode Redundancy

VC Virtual Channels

VHDL Very High-Speed Integrated Circuit Hardware Description Language

# **Acknowledgements**

It's been a long time coming and I'm sure those close to me will know how happy it makes me to finally be here, concluding a chapter of my life. It has been an enormous effort, like that of Sisyphus, but less dramatic.

First of all, I would like to pay homage and thank those directly involved with my PhD. Dr. Jim Harkin, Professor Liam McDaid, Dr. John Wade and Dr. Junxiu Liu, without their work, wisdom and support I would never have made it this far and for that, I am indebted to them. To my friends and colleagues within the ISRC, thank you sincerely for the support, for the friendship, for the coffee breaks and the football, which were sometimes the means to an end.

# **Dedication**

To my friends and family, for every day I had doubts and every day that I doubted myself, I dedicate this to you, you kept me going. To my father, George Martin and my godfather Stephen Martin, your support kept my feet on the ground and made sure I never lost sight of what was important. To my late grandfather George Martin and grandmother Anne Martin, I owe a lot to you, you showed me how love and hard work can overcome humble means. To my mother Catherine Cosgrove, without you none of this would have been possible, and finally my sister Corrina and her children Lucas & Khloe, and my brothers Christopher, Carlos and Thomas.

"It is not the critic who counts; not the man who points out how the strong man stumbles, or where the doer of deeds could have done them better. The credit belongs to the man who is actually in the arena, whose face is marred by dust and sweat and blood; who strives valiantly; who errs, who comes short again and again, because there is no effort without error and shortcoming; but who does actually strive to do the deeds; who knows great enthusiasms, the great devotions; who spends himself in a worthy cause; who at the best knows in the end the triumph of high achievement, and who at the worst, if he fails, at least fails while daring greatly, so that his place shall never be with those cold and timid souls who neither know victory nor defeat."

- Theodore Roosevelt

# **Chapter 1: Introduction**

# 1.1 Background

Computing has advanced every aspect of our species from exploring the universe, the curiosity rover on Mars [1] and Juno on Jupiter [2], to the human brain exploring how the brains processes information in a fast and efficient manner. Scientists and engineers look to biology for inspiration. Over recent years humans have pushed the boundaries of computing and the technology used for computation. Computational performance using central processor units (CPUs) allows computers to perform a large number of calculations sequentially, therefore, computers can be used to solve complex problems. The hardware is based on sequential computing using single core processors and it is therefore limited; it is power hungry and inefficient because it performs calculations one after another. Using multiple CPUs can allow computers to operate with some parallelism but it is limited. The brain uses its innate parallel infrastructure to process information and this is much faster and much more efficient for complex problem solving. More recently, research has been carried out to mimic how the brain processes information using the timing and frequency of spikes to encode information [3]. Neurons process information in highly parallel manner, harnessing huge amounts of processing power efficiently. Models have been derived to replicate and emulate neurons and how they process information, and although these models are evidently based on biology, (i.e. neurons and human brain performance) there is still a lot to be desired i.e. NN applications cannot compare to the brain in regards to pattern recognition challenges such as visual and speech recognition [4], [5] as they don't have the same performance, are inefficient in terms of both time and computational power. This is because neural network applications use supervised learning for classification, this requires training, and due to the vast amount of data it is mostly done offline. Training requires the user to input data and "train the network" by using labelled outputs, another downfall is that software approaches lack efficiency and use up computational resources. Neural networks typically have one application specified by the user.

SNN applications overcome the computational and performance bottlenecks of traditional NNs and are based on how the brain processes data. SNNs differ from traditional NNs as information is encoded in spikes, this is more efficient and analogous to how the brain processes information but again the network is trained offline before it can be deployed. There is also the issue that simulating SNNs on hardware is computationally intensive but Neuromorphic hardware such as TrueNorth aims to replicate inherent parallelism by using hardware which deviates from traditional Von Neumann architecture as each neuron has memory, computational power and a communication aspect. There are however promising real-world applications of SNNs in audio processing [6] and image processing [7].

Self-repair is highly sought after in electronic systems due to technology becoming much smaller in size (geometric scaling), resulting in electronic systems becoming more prone to faults [8]. The ability to repair and tolerate faults leads to more reliable and robust systems. To maintain functionality and increase operational lifetime of an electronic system, a method of fault tolerance or self-repair is required [9]. Current fault tolerant mechanisms are based on coarse grained redundancy and employ the use of a central repair-decision agent to either find faults or correct them, such as Triple Mode Redundancy (TMR), which is typically used in mission critical systems [10]. TMR is the process of replicating critical components and using a comparator to detect discrepancies. This vastly increases area overhead and relies heavily on spare or redundant computing resources. The key weaknesses of existing approaches is limited granularity and the lack of a distributed repair-decision mechanism.

SNNs typically run on specialised hardware, this hardware is typically deployed in harsh environments and therefore, the hardware must use a form of fault tolerance. Rather than look at the electronic hardware, an SNN has neurons connected to a number of inputs; the network is trained to classify this data based on the inputs and information is passed via a huge number of synapses. Although the SNN may be susceptible to electronic failures and faults e.g. a sensor failing; rather than becoming completely useless, it is possible to employ what can be considered as a graceful degradation.

Recent research has shown that biological traits such as fine grained repair and distributed repair-decision making are performed in the brain via networks of glia cells (astrocytes) [11], [12]. It has been said there are 100 billion neurons and one trillion glial cells, with a glia to neuron ratio of 10:1. Even though such estimations are debated [13], it is the inherent parallelism and features such as fault tolerance and low-power consumption that have us look to the brain for inspiration. It has been discovered that astrocytes within the brain mediate synaptic plasticity [14] and this allows astrocytes to actively increase or decrease the probability of release (PR) of a synapse. Self-repair can be observed across faulty synapses when the PR on healthy neuron-synapses is increased, i.e. firing activity can be repaired to pre-fault levels, even with a substantial amount of faults (80%) [12].

In particular, computational models of such repair have been successfully captured and applied to spiking neural networks (SNNs) [15]. An SNN is a neural network which uses the timing and frequency of spikes to propagate information; a spike train is used to encode information. The research in [15] demonstrates how low neuron firing activity can be repaired at fine-grained levels, i.e. the synapses. The healthy synapses can be strengthened which enables the neuron to regain functionality (spiking). This can result in self-repair across the spiking neural network. The cell responsible for self-repair has been identified as the astrocyte. Astrocytes are highly distributed within networks of neurons [15]. This neuro–glia network paradigm addresses the key self-repair requirements of fine granularity and distributed decision making and this sets the focus of this PhD research.

There are a number of difficult challenges to overcome in order to realise a neuro-glia network in hardware:

- The realisation of both local and global communications within a neuro-glia network. Using astrocytes and providing self-repair requires a hierarchy of communication.

- Applying self-repair within a neuro-glia network is two separate networks working in unison; an SNN and an astrocyte network. There are additional interconnect

requirements including additional complexity and communication. This is a neural network with the functionality of an SNN for classification and astrocytes for self-repair, therefore, this application of self-repair is applied within an existing SNN framework.

• The scalability requirements, as the network scales the communication infrastructure must support the additional processing and communication requirements. The timing of communication between neuron and astrocyte networks diverges; a neural network emphasises throughput. The astrocyte is a lot slower process which focuses on self-repair and supporting the network and synapses. The network must be able to accommodate both communication processes and keep these working in unity.

One of the key challenges in progressing neuro—glia networks to hardware is connecting a network of astrocytes with an SNN. Astrocytes connect to groups of synapses and also form large networks of their own. Emulating a neuro—glia network in hardware introduces additional challenges such as increased complexity of the network, increased wiring interconnect overheads to maintain communication within a network and dealing with different time scales between neurons and astrocyte. There, we seek a scalable method of interconnecting astrocytes to astrocytes, and astrocytes to neurons, i.e. realise a low area and power strategy.

Networks-on-Chip (NoC) has emerged as a scalable approach for interconnecting many cores on a single chip, and is based on network engineering approaches over physical wires, buses and crossbars [16]–[18]. Therefore, we can look to exploit this mechanism in a manner which facilitates scalable data exchanges between neurons, synapses and astrocytes. This thesis explores the following:

#### **Objectives:**

1. Can HW models of networks of glia cells be successfully scaled using network on chip architecture?"

- 2. Is a ring-topology suitable for astrocyte to neuron and astrocyte to astrocyte communication at the low level of a network on chip hierarchy?

- 3. Is this topology capable of enabling both fault tolerance capability in synaptic connections and overall network scalability?

#### 1.2 Thesis Contributions

This thesis covers a substantial body of research into self-repair. This self-repair is an innate feature of the human brain, provided by astrocytes. This thesis proposes using bio-inspired hardware within an existing neural network framework using on-chip interconnect strategies. That is, research into how the astrocyte process works and communicates with neurons and combining the features of astrocytes with neural networks, more specifically SNNs and H-NoC. The resulting contributions are the initial steps into realising large scale neuroglia networks using existing features of SNNs combined with a digital astrocyte in hardware thus exploring neuro-glia networks using a scalable field-programmable gate array (FPGA) interconnect.

The contributions presented within this thesis are:

- A novel NoC interconnect based on using a ring topology to communicate e –SP for local communication in a neuro-glia network between neurons and astrocytes.

This trades off area for communication speed (Chapter 5).

- 2. Detailed analysis of area and scalability, in regard to keeping low hardware overheads using a ring-based topology using NoC (Chapter 5).

- 3. Applying this interconnect for local commutation between astrocytes and neurons within an existing framework: Hierarchical Network on Chip (H-NoC) (Chapter 5).

- 4. A novel NoC router for global communication in a neuro-glia network in astrocyte networks. The astrocyte router is based on using a ring topology and uses low level logic to average and communicate IP<sub>3</sub> to all associated astrocytes (Chapter 6).

- 5. An analysis of area, power and scalability using an astrocyte tile router for communication between astrocytes. A trade-off between the biological time scale and low overheads in hardware (Chapter 6).

- 6. Validating the NoC interconnect in FPGA hardware using an example mobile robotic car (Chapter 7).

#### 1.3 Thesis Outline

The outline of this thesis is as follows:

**Chapter 2** provides a review of self-repair, astrocytes and neurons, and their role in computational software and hardware. From the biochemical reactions to computational neural networks, i.e. from biology to hardware. This provides an insight into the biological and computational motivation behind self-repair.

Chapter 3 investigates the application of the NoC paradigm as a hardware interconnect capable of providing a large-scale neuro-glia network with desired scalability. The chapter initially reviews NoC features, from topologies to existing NoC solutions in hardware. A review of current methods of fault tolerance and self-repair as well as a review of mechanisms already in place to facilitate self-repair is also provided. There is also a review of biological self-repair and the aim of implementing this self-repair process in a Neuro-glia network. The latter part of the chapter focuses on the challenges of implementing a neuro-glia network using a NoC interconnect.

**Chapter 4** highlights why self-repair is desirable and why to date, current self-repair or fault tolerant approaches come at large overheads e.g. TMR. In particular, biologically inspired self-repair has been recently shown to provide fine grained and distributed self-repair using computational models, but due to limited scalability and performance constraints, require more creative, high performance and robust means to explore further.

**Chapter 5** outlines the interactions and communication exchange between neurons and astrocytes, this being a local communication exchange. This chapter contributes a novel low-level NoC ring topology which facilitates astrocyte to neuron communication. The main focus is on the steps taken to implementing a ring topology and communication protocol. The results show that the e-SP ring provides a low area scalable interconnect solution to communicating e-SP to associated neurons within a node facility.

Chapter 6 addresses global interactions of a neuro-glia network and astrocyte to astrocyte interactions in hardware. It provides an overview of the interactions and communication exchange between astrocytes as a network, this being a global communication exchange. The main focus is on the steps taken to implementing a novel astrocyte router. The astrocyte router connects eight astrocytes in a ring topology and uses serial communication, trading off speed for area. The router uses a novel dynamic scheduler and token system to manage the synchronous aspects of astrocytes within the astrocyte network balancing urgency using timing and token requests as thresholds. This is to provide communication protocol for future use in neuro-glia networks, thereby providing a scalable solution to this interconnect challenge. FPGA results demonstrate the astrocyte router provides a good trade-off between low area and low power to interconnect overhead and relatively low communication speed.

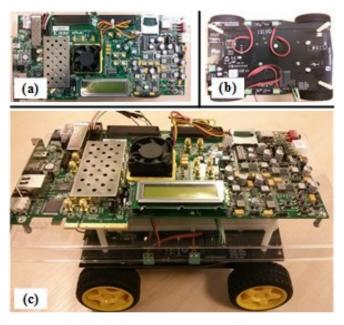

Chapter 7 presents results on hardware validation of the interconnect strategies and demonstrate the self-repair functionality in FPGA hardware using an example: a mobile robot. The chapter reviews this mobile robot which uses a spiking astrocyte-neuron network. The ring topology (Chapter 5) is applied to the existing hardware to communicate signalling data to provide the neural network with a self-repair capability. This is a real-world application of a SNN with self-repair and results are presented that show that if the synapses within the neural network are faulty, the neuro-glia network has the ability to adapt and repair and maintain the direction and speed. Results have shown that with up to 80% of faulty synapses the network can repair and restore pre-fault functionality.

**Chapter 8** draws a conclusion to the thesis and discusses the contributions. There is also a section indicative of future work which may be carried out to extend the research presented in this thesis.

#### 1.4 Publications

This section presents the papers and publications which have been peer-reviewed publications in conferences and journals during this thesis:

# 1.4.1 Conference papers

G. Martin, J. Harkin, L. J. McDaid, J. J. Wade, J. Liu and F. Morgan, "Astrocyte to spiking neuron communication using Networks-on-Chip ring topology," IEEE Symposium Series on Computational Intelligence (SSCI), Athens, 2016, pp. 1-8. (Contributes to Chapter 5).

J. Liu, J. Harkin, L. McDaid, and G. Martin, "Hierarchical networks-on-chip interconnect for astrocyte-neuron network hardware," ICANN 2016: Artificial Neural Networks and Machine Learning – ICANN 2016 pp 382-390, Lecture Notes in Computer Science

# 1.4.2 Journal Papers

G. Martin, J. Harkin, L. J. McDaid, J. J. Wade and J. Liu, "On-chip communication for neuro-glia networks," IET Computer Digital Techniques: Special Issue Bio-inspired Hardware and Evolvable Systems, vol. 12, no. 4, pp. 130-138, 2018. (Contributes to Chapter 6).

J. Liu, J. Harkin, L. P. Maguire, L. J. McDaid, J. J. Wade and G. Martin, "Scalable Networks-on-Chip Interconnected Architecture for Astrocyte-Neuron Networks," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 63, no. 12, pp. 2290-2303, Dec. 2016.

# 1.5 Summary of contributions

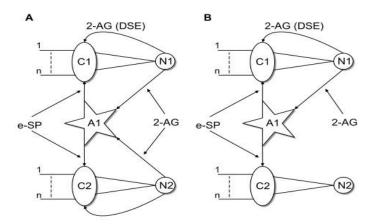

Local Communication: This contribution is a low-level NoC interconnect based on a ring topology. This focused on the excitatory signal from an astrocyte, i.e. e-SP. This signal is a product of the astrocyte, which is connected to neurons within a neural network. The e-SP is produced to provide an equilibrium across the synapse. It reinforces the PR on healthy synapses, which restores pre-fault firing activity in neurons. This work included an overview of H-NoC which was the existing SNN hardware used to stimulate the astrocyte by cloning packets and forwarding these packets to the astrocyte. The astrocyte then responded to the stimulus and produced 2-AG and subsequently e-SP. This e-SP is the excitatory signal which increases PR in a healthy synapse, this signal was communicated back to the astrocytes within the Node Facilities of H-NoC. The H-NoC paradigm is a scalable SNN, and using this existing framework it was possible to provide a scalable interconnect to communicate between an astrocyte and the SNN. The ring topology provided a scalable self-repair interconnect solution within a Neuro-glia network.

The low-level communication paradigm between a network of astrocyte cells and an SNN is realised in this contribution using a ring-topology. This supports parallelism as it requires normal SNN activity whilst supporting low-level interactions between spiking neurons. This low-level communication from the astrocyte occurs between each astrocyte and the SNN network. Neurons communicate with a sequential and time-based method, whereas, astrocytes communicate continuously at a much slower rate. Astrocyte data is numerical in value and to retain the precision of computational models, the bit resolution is 64-bit. As the signal is large and the network is vast, this provides an interconnect problem and it is necessary to adapt the interconnect thereby making it suitable for applying to neuro-glia networks in hardware. This e-SP ring topology allows an astrocyte to communicate e-SP within an existing SNN and this interconnect provides a scalable solution for low level communication between an astrocyte and neurons within a neuroglia network. Within the astrocyte there is a lot of data exchanged at a less demanding throughput compared to that of spike events. In engineering terms, this slow continuous exchange of information can be exploited to save on area. This contribution also provided a solution for communication exchange between neurons and astrocytes at a local level

(inter-astrocyte) interchange using a NoC ring topology to exploit the slow changing communication in order to provide a low area interconnect capable of scaling for large scale networks.

**Global Communication:** As well as communicating with neurons, astrocytes also communicate within networks of astrocytes via a global communication protocol. This communication protocol within the neuro-glia network can be considered a multi-level communication which supports both local and global communication exchanges. The global astrocyte-to-astrocyte interchange communicates IP<sub>3</sub> data. Within an astrocyte, IP<sub>3</sub> oscillates and this causes a trigger to allow Ca<sup>2+</sup> to be released.

This process balances glia-transmitters across all associated and neighbouring astrocytes. The network detects changes in IP<sub>3</sub> and this is communicated across all connected astrocytes. As astrocytes influence and affect each other, it removes the need for a central controller. It is this distributed and complex communication which allows self-repair on a global scale.

The astrocyte receives stimulus from the SNN. This event data is communicated from H-NoC to the astrocyte via an additional output port within the node router of H-NoC. The astrocyte model receives spikes from neurons which stimulate the release of 2-AG and the astrocyte produces the IP<sub>3</sub>, DSE and e-SP signals. As IP<sub>3</sub> is a global communication signal it is shared across its neighbouring astrocytes. Each astrocyte has a level of IP<sub>3</sub> and any changes in this IP<sub>3</sub> indicates either increased or decreased levels. Astrocytes function by balancing and sharing their levels of IP<sub>3</sub> to ensure that there is enough IP<sub>3</sub> to facilitate repair and maintain normal functionality. This contribution is a multi-level solution for communicating signals (both local and global).

The global signal from each astrocyte is connected to an astrocyte tile router. The astrocyte router has two main roles: (1) receive IP<sub>3</sub> level data from up to eight astrocytes and, (2) calculate the average IP<sub>3</sub> level for all eight astrocytes and communicate this back to all eight. The rate at which IP<sub>3</sub> changes is much slower than spike events; typically 2-

3 orders of magnitude slower. Therefore, this contribution provided a hardware interconnect focused on balancing the physical area per astrocyte tile router facility while also meeting real-time requirements of the IP<sub>3</sub> exchange and update process. The astrocyte cluster facility is also an important component of the overall architecture of the astrocyte router. The ring topology in NoCs has previously shown benefits in area-speed trade-offs for area for both SNN and neuro-glia hardware. By exploiting the slower communication speeds of the biological IP<sub>3</sub> signal a time-multiplexed approach using ring structures can reduce area and power overheads. This contribution provides a scalable solution for global communication exchanges in neuro-glia networks.

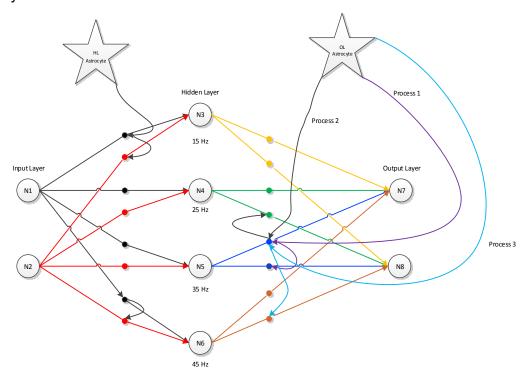

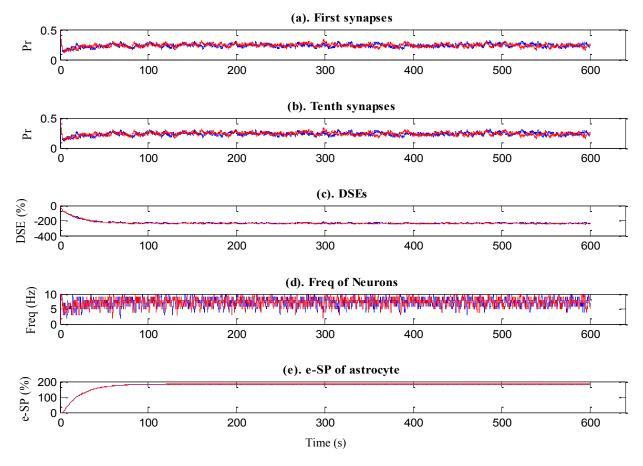

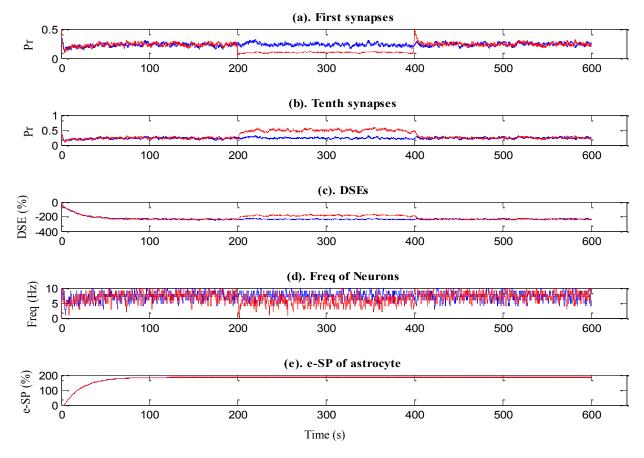

Hardware Validation: The e-SP ring topology from contribution 1 is applied to a SANN. The astrocyte releases e-SP to strengthen PR and facilitates self-repair. When the e-SP strengthens the remaining healthy synapses the firing activity of the neuron is restored. The SANN is developed on an FPGA and consists of two neurons (Neuron #1 and #2), associated synapses and the astrocyte process. The neurons generate 2-AG which splits into two signals (e-SP and DSE). DSE goes to the astrocyte and reduces the PR on all synapses. The astrocyte then generates e-SP which increases PR on all synapses. The output spike from each neuron, is converted to an output frequency by a PWM and Neuron #2 controls the speed of the robot from this output frequency. Within this model there are no faulty synapses associated with Neuron 1, the faulty synapses are associated with Neuron 2. These are injected with faults during normal operation. The first to eighth synapses associated with Neuron 2 can have faults indicating the percentage of faulty synapses. When faults have been detected, the PR in associated synapses falls, and the e-SP rises. As the healthy synapses increase PR, the frequency of neuron #2 begins to recover to a pre-fault frequency.

The SANN can be broken down into two neuron facilities, two synapse facilities and an astrocyte facility. While 64-bit precision has a large overhead, it is used so that the system output can be compared against the computer simulated models. The first step in realising the e-SP with large scale astrocyte-neuron networks is to work within a biological timescale and so, the 'e-SP comms' module was integrated into the SANN. The e-SP

data comes from the astrocyte and is used as input data to the synapse facilities. The e-SP ring takes the e-SP output from the astrocyte and sends it to the associated synapses at each neuron. Results show that within the SANN with the e-SP ring in place, there is no deviation of results when compared to the SANN model hardware without the ring when additionally using the ring in hardware. The output frequency and the e-SP incurred overhead show quantifiable results directly affected by the e-SP ring within the SANN. These results show that although the ring focuses on a low-level serial communication protocol it is able to maintain accuracy compared to software models and similar accuracy when applied in hardware.

# **Chapter 2: From biology to hardware**

#### 2.1 Introduction

If a system is deployed to space and is unable to complete its mission due to a simple fault, it is a failed mission. In recent years, fault tolerance and self-repair have become a key research field especially in mission critical systems such as avionics and space applications, due to harsh environments [19]. Self-repair is a desired characteristic in such systems. This is because the device may repair its own faults, repairing or overcoming the fault or component, and returning to functional operation, or to some degree of acceptable performance.

Recent research has shown that biological traits such as fine grained repair and distributed repair-decision making are performed in the brain via astrocyte networks [11], [12]. In particular, computational models of such repair have been successfully captured and applied to SNNs [15] where neuron activity can be repaired to near pre-fault operation via the re-strengthening of the neuron's healthy synaptic connections. Since the repair occurs at the individual neuron synapses, this fault detection and repair is at a fine-grained level. The mechanism which makes the repair-decision within the brain has been identified as the astrocyte process, which is a type of glial cell highly distributed within networks of neurons [15]. This neuro-glia network paradigm addresses the key self-repair requirements of fine granularity and distributed decision making and sets the focus of this thesis. One of the key challenges in progressing neuro-glia networks to hardware is connecting a network of astrocytes with an SNN. Astrocytes connect to groups of synapses and also form large networks of their own. Therefore, emulating a neuro-glia network in hardware introduces additional interconnect challenges which also requires maintaining a scalable, low power/area overhead implementation. This will support a more complete understanding of the human brain, and the information exchanges, as well as providing biologically inspired self-repair for electronic systems.

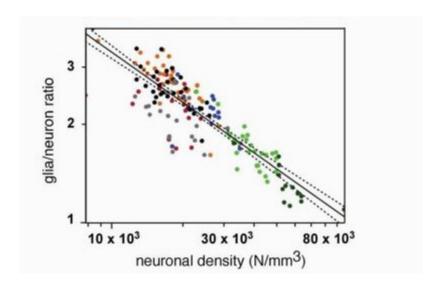

# 2.2 Neural information processing

The brain is mainly made up of neuron and glial cells where early studies suggested that the neurons were considered to the main functioning cell whilst glial cells solely provided structural integrity. More recent research however, has shed light on the inner mechanisms and complexity of the brain. It was perceived, and accepted, that an adult had approximately 100 billion neurons and 10 times as many glial cells, but, this figure is closer to 86 billion neurons [20]. Interestingly, a study identified on average, the number of cortical neurons in new-borns was similar to that of an adults however, the number of glial cells was found to be approximately one-fifth to one-sixth to that of an adults total number of glial cells [21]. With more and more research, we unlock secrets within the brain, yet there is so much to understand. There are between 6-10 neurons to one astrocyte according to recent research [13]. This is discussed in more detail in Chapter 6. Section 6.2.1 Neurons and glia cells.

The Human brain is highly efficient and has the ability to process information efficiently using around 12 Watts of power [22], [23]. 108 times faster than traditional computers [24] and highly adept at problem solving, pattern recognition and performing cognitive functions [25]. Traditional computers, although fast when carrying out sequential operations, struggle with pattern recognition and other complex problems (such as data processing and classification). They are inefficient in terms of computational power and power consumption. One such model, the blue brain project, using the IBM Blue Gene/L supercomputer has 8,192 CPUs running at a clock frequency of 700MHz and at peak performance, should provide 360 teraflops. This was published in 2006 [26], since then Blue Brain has been updated: Blue Brain 4 was released in 2014 and more recently Blue Brain 5 was released in 2018 (see section 2.4.1). Within the brain, it is the parallel infrastructure and the interconnect between neurons and how they communicate, which provides efficient and powerful processing.

#### 2.2.1 Neurons

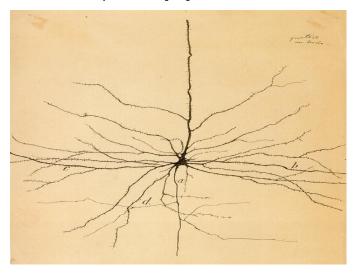

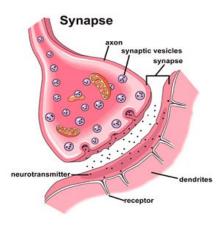

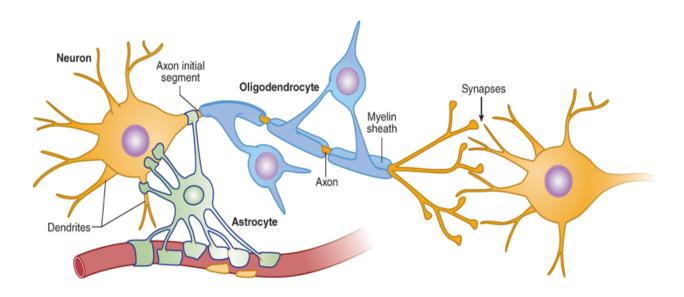

Beginning in the early 1900s, the structure of neurons within the brain began to be explored, Fig.2.1. Shows Santiago Ramón y Cajal drawing of very early depiction of a neuron. The neuron is the main cell responsible for communicating information [27] and is made up of several components: the soma, axon, dendrite and synapse. From a simplistic viewpoint, the dendrites are inputs and the axon is the neuron's output (a neuron may have many inputs but only one output which branches out to many other neurons). Fig.2.2. Shows a synaptic cleft connecting an axon and dendrite, this is a chemical exchange between neurons. Fig.2.3. Depicts a more recent illustration of a neuron; labelling the neurons various components [28].

Fig.2.1 A neuron by Ramon y Cajal [29].

Fig.2.2 Synaptic cleft [30].

Fig.2.3 A closer look at the neuron. Here are the individual components of a neuron and connected to an astrocyte cell.

To understand how a neural network processes information we must first look at these individual components and their operation during a spike event i.e. the communication protocol between neurons [27]. The neuron body is referred to as the soma. This soma is made up of positively and negatively charged ions, but sodium (Na<sup>+</sup>) and potassium (K<sup>+</sup>) are the most important in neural computation and communication. These channels were first identified in the nerves of a giant squid when Hodgkin and Huxley dissected a giant squids nerves and applied electrical current to observe and explore the nature of neurons and their communication channels [31]. Information from neighbouring neurons stimulate the soma. This information arrives from the dendrites and cause a chemical reaction to occur which then causes an electrical reaction.

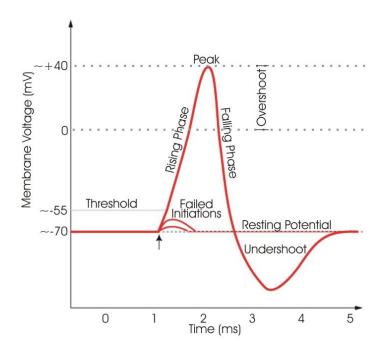

This reaction is caused as sodium channels open and the positively charged sodium ions flow through the membrane and into the soma, this is known as depolarization. The membrane potential has a voltage threshold (typically between -50 and -55 mV), as the neuron receives stimulus the membrane potential increases until it breaches the said threshold. This causes a spike or action potential (AP) to output through the axon to the synaptic cleft and into another neuron, i.e. a surge of glutamate across the synaptic cleft

[23], [32]. The axon is considered the output of the neuron and is connected to a dendrite via the synapse or synaptic cleft. Repolarization follows when the potassium channels open to allow potassium ions to leave the soma and restore membrane potential, this is the refractory period where the neuron is unable to fire again regardless of stimulus. Fig.2.4 is an action potential showing depolarisation and repolarisation.

Fig.2.4 An AP/spike [33].

#### 2.3 Neural networks

A typical neural network consists of artificial neural cells interconnected in a predefined topology with input and output layers and these layers consist of multiple inputs and outputs. The main aim of a neural network is to emulate an artificial system capable of complex problem solving and pattern recognition analogous to the brain, in a highly efficient parallel system. A neural network can be broken down into 3 main components: the I/O (input and output) layers, the interconnect or topology connecting neurons and the ability to learn. Recreating the architecture of the brain in a neural network with the capability to learn, brings us closer to solving more complex problems. Neighbouring neurons communicate via spikes, as the number of input spikes accumulate, the stimulus

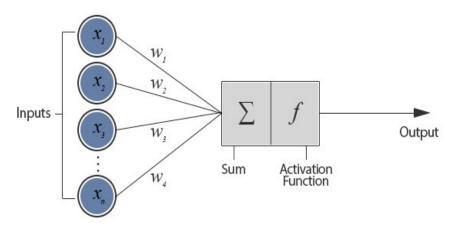

surpasses a predefined threshold causing the neural cell to fire i.e. releases a spike. This emulates the neurological process and therefore is analogous to the biological neurons and their communication protocols [27], [28]. Fig.2.5. shows a simplified overview of an ANN. In this case the input  $(X_n)$  is multiplied by the weight  $(W_n)$  of the synapse and the sum of the inputs is compared to an internal threshold (activation threshold). If the sum of the inputs passes the threshold value, the output is 1, if not it remains 0.

Fig.2.5 Simplified overview of an ANN [34].

Neural networks can be regarded as having three generations, the first- and second-generation models use rate coding, and these models were based on using the number of spikes to communicate. The McCulloch and Pitts model is considered the first generation of artificial neural network (ANN). The threshold for the firing rule (activation function) of the neuron is based on a step function. Neurons exchange information with neighbouring neurons and each input is multiplied by a weighted sum. If the sum of the vector surpasses the threshold, the neuron then fires a binary 1 or 0 [35].

Donald Hebb (Hebbian theory), proposed an explanation for the adaptation of neurons in the brain during learning, "Cells that fire together wire together". This is unsupervised learning. The causal link between neurons is strengthened based on the firing activity i.e. the weights associated with each synapse were updated based on the firing activity of the neuron. Reinforcing the relationships between connected neurons, the network would adapt and learn based on activity [36]. The second generation of ANNs, furthered the work

on neural networks by way of learning. In 1958, a Single Layer Perceptron (SLP) was introduced. This used supervised learning to update the weights associated with neurons. Supervised learning uses training examples to associate an input to an output based on a training set. The user supplies a training set, and an expected output, to train the network, and then supplies a completely new set. The supervised learning should allow the network to classify new data correctly. By modifying the synaptic weights and threshold function, it is possible to perform pattern recognition [37].

Although the simplicity of using a SLP was a principal feature of such networks, they were unable to solve the basic XOR problem [38]. It was hypothesised, that introducing a hidden layer and devising a Multilayer perceptron (MLP) based on error back propagation, would solve the XOR problem. The trade-off of this approach was an increase in the complexity of the model, diminishing the simplicity of the SLP. A neural network may have a number of layers between the inputs and outputs, generally referred to as hidden layers. The number of layers depends on the classification or purpose of the network. An interesting aspect of the first and second generations of neural networks was that they focused on using the rate of spikes. However, this ignored the timing of the spikes completely. This leads us to the third generation of neural networks, a Spiking Neural Network (SNN). SNNs use the timing and frequency of their spikes to encode information. That is, they encode information based on the timing of spike events and/or rate coding. They communicate as such to neighbouring neurons, this is similar with how the brain processes information or data as spike events propagate from neuron to neuron [39], [40].

# 2.3.1 Spiking neural networks

As mentioned previously, SNNs are based on sending information between neighbouring neurons using the timing and frequency of their spikes (temporal and rate coding) rather than using the spikes shape or size [41]–[43]. SNNs can be used to carry out more complex computations and they are a more accurate representation of how neurons communicate based on biological evidence. However, it has become increasingly difficult to simulate large scale SNNs because of limited scalability when realizing the complex

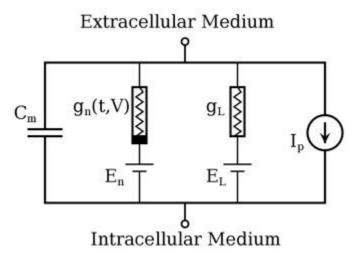

interconnect [44] and as such there is trade-off between complexity and biological plausibility [45]. There are several computational models based on using the timing of the spikes to encode information. Hodgkin and Huxley, based on the nerve cell of a giant squid, found that the nerves consisted of a membrane sheath consisting of sodium and potassium currents as well as a leak current, as seen in Fig.2.6 and thus produced an accurate mathematical model of a neuron. This is the Hodgkin–Huxley model of the characteristics of cell membranes [31].

**Fig.2.6** Hodgkin and Huxley model. This model uses voltage-gated ( $g_n$  and  $g_L$ ) and leak channels to model the dynamics within a neuron [46].

The Hodgkin and Huxley model has four differential equations and as a result, the mathematical model is computationally intensive due to the number of variables [23]. There have been attempts to recreate a similar model without the computational complexity but without reducing the accuracy. The Integrate and fire (IF) model based on the most basic concept of a biological neuron consists of a single capacitor which represents the charging capacity of a neuron. When current is injected, the capacitor will charge until it reaches a voltage threshold and then discharge. This can be viewed as analogous to a spike [42]. The Leaky integrate and fire (LIF) model, goes a step further and provides the model with a resistor which represents the leak current. Each time a spike activates current, the capacitor charges, the resistor then causes the capacitor to lose this charge if there is no further stimulation. This simple model is similar to that of a neuron, with no spikes or voltage input into the neuron model, the charge returns to

resting potential [23]. Although very simple approaches, they maintain the most important aspects of a neuron model, that is the charging and leaking aspect. Other examples of computational models based on SNNs include: Spike Response Model (SRM) [23], and Izhikevich [39], amongst others. Interestingly, the Izhikevich model is a biologically plausible mathematical model and is capable of reproducing all different firing patterns exhibited by cortical neurons. It consists of two differential equations and this model can give a realistic insight into cortical neurons interacting with one another [39].

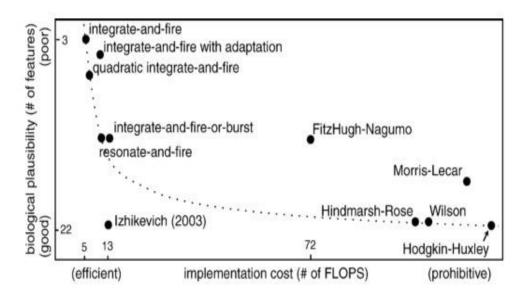

Due to the number of computational SNN models available, it is difficult to distinguish an overall "best" model. There are a number of key differences and ultimately it becomes, biological plausibility vs computational complexity as seen in Fig.2.7. [45]. The choice and selection of a neuron model depends on the purpose of the model and the amount of computational resources available. If the purpose of a model is to identify neural dynamics or the behaviour of neurons and how they interact and communicate, a Hodgkin and Huxley (HH) [31] model or Izhikevich model [39] may be used but will result in a smaller scale network i.e. having smaller numbers of neurons but with greater complexity. If, however, the purpose is to view the interconnect strategies between neurons on a large scale, the biophysical complexity of the model is sacrificed in order to increase the number of neurons and have a larger network. Therefore, the computational resources available can be applied to other aspects of the network e.g. the number of neurons or identifying interconnect topologies.

Fig.2.7 Biological plausibility vs computational complexity [45].

# 2.4 Neural networks: computational implementations

There are many reasons to model and investigate how the brain processes information. It may give a much better understanding of how a parallel dense interconnect populated with neurons can lead to huge data processing abilities or how to harness such processing power of such a simple model with an efficient power consumption [23], [42]. Alternatively it could allow the exploration of degenerative diseases that plague the brain such as epilepsy, Alzheimer's and Parkinson's [47]. Using models for more efficient processing systems capable of big data, speech recognition and pattern recognition, will lead to better systems in the future in terms of research within medicine [48]. It could also give us insight into other cells at work within the brain, as it has done with astrocytes [49].

#### 2.4.1 Neural networks in software

Software applications offer researchers the flexibility of choosing complex or simplified models based on the nature of the research. It allows customisation throughout the network from start to finish, meaning the network can be specifically applied for certain problem solving or classifying purposes. Software models are also very useful for

investigating more complex neural networks and how neurons communicate in different parts of the brain e.g. the neocortex [45], and neuron models help explore the behaviour of neurons more closely. The biggest drawback of using software models is the processing power. The power required to explore and develop these models, is not always available off-the-shelf. In terms of software, modelling NNs suffers due to the hardware bottleneck used to create and run applications. This is due to sequential processors unable to execute parallel networks efficiently, this leads to an inefficient and power hungry processing [50]. There are two main platforms for realising neural networks in software using traditional processing units, general purpose Graphic Processor Units (GPU) and High-Performance Computers (HPC) [51]. A hybrid approach may also be considered using CPUs with specific NN hardware in order to accelerate the neural network applications [52]. In recent years, processing power and performance has increased significantly. The off-the-shelf Intel i9-7980XE 18-core, 36-thread CPU, clock speeds vary from 4.2GHz to 3.9GHz up to 12 cores, is due to be released Fall 2018 [53]. It would seem that the resources for neural networks on traditional CPU architectures may not be far away however, GPUs consist of more processing cores and dedicated processors to that of general-purpose CPUs. Graphics processing units, typically containing a lot more cores which makes them more suitable for realising the parallelism of neural networks than CPUs, and examples of such software simulations have been used in the past [54], [55]. General-purpose computing components aren't sufficient and are very limited in regard to simulating neural networks. These vast neural networks consist of only hundreds of thousands of neurons and synaptic connections, which would allow a very small-scale realisation. NeMo used a general purpose GPU to simulate one million neurons, with 1000 synapses each, firing at 10 Hz [54]. A GPU out-performs a CPU, but they are still inefficient and power hungry as well as slow [50]. It is the parallelism that researchers struggle to re-create. NCS6 was able to simulate one million cells and 100 million synapses by distributing data across eight machines with each having two video cards [56]. A CPU cluster e.g. Beowulf cluster which is a network of computers [57], similarly, GPUs can exploit their cores for parallelism, which can be used in realising NN models [57].

HPCs allow the realisations of large-scale neural networks with flexibility in terms of programming and creating networks, in [57] a computational model of the *thalamocortical* system was simulated on a Beowulf cluster. This simulation comprised of one million neurons and half a billion synapses. In computational terms, there were sixty 3 GHz processers, each with 1.5 GB of RAM yet, could not match real-time performance of biological systems. They aim to allow the user to modify the number of neurons, the number of hidden layers and the parallel interconnect.

HPCs can be used for deep learning, and are made up of combining GPUs, however, they have limitations such as scalability. In [58] a HPC capable of training one billion parameter networks was described but encountered scaling problems when trying to exploit parallelism across multiple GPUs. In [59] a Titan supercomputer was used in order to optimize the performance of deep learning algorithms. As the size of the network grows, the hyper-parameter space grows increasingly larger. Other such HPC approaches look to accelerate training using HPCs e.g. Caffe-HPC aims to train large models [60] using a HPC approach. So although HPCs can be applied to reduce certain aspects such as training times or accelerate models, they are limited.

With increasing numbers of neurons and additional complexity, the software simulations become more difficult to simulate and realise. As a result, this uses more computational resources available [26]. HPCs contain huge reservoirs of computational resources, allowing increasingly complex neural networks, but they are slow and do not scale efficiently when realising large scale SNNs [61]. Computational models have proven very effective at pattern recognition (speech and facial recognition), classifying biological information using neural networks [48]. SNNs have been emulated in software with the aim of creating a highly parallel implementation for acceleration purposes [8], [62], [63] and also as exploratory platforms [64], [65]. The BlueBrain project [26] is an example of a software implementation using a HPC.

The Blue Brain 4 and Blue Brain 5 are installed at the Swiss National Supercomputer Centre (CSCS). Blue Brain 4 aimed to simulate a rodent's brain (200 million neurons). The

Blue Brain 4 comprised of a four-rack IBM BlueGene/Q system 65,536 cores for computing, providing a peak performance of 839 Tera Flops [66]. The Blue Brain 5 core system is an HPE SGI 8600 system comprised of 372 compute nodes, providing 1.06 petaflops of peak performance. [67].

Software approaches are flexible due to the software control but exhibits significant physical space, cost and power overheads. In regards to software, the key challenge for implementing SNN software models on typical processing hardware is scalability. This stems from the need for efficient interconnect wiring, low area/power synapse and neuron designs, efficient weight storage, programmability of SNN topology and weights. It is the inability to do this without huge amounts of computational resources that make it very difficult to make an efficient neural network in software which can perform simulations in close to biological real time.

#### 2.4.2 Neural networks in firmware

It is natural to progress to a hardware platform as a solution to the software approach's short-comings; researchers considered using Field Programmable Gate Arrays (FPGAs) [68], [69].

FPGAs provide a solution to the inherent problems of using software i.e. the hardware bottlenecks. Simulating large scale neural networks on a hardware platform, removes the limited CPU and GPU overheads as FPGAs are more efficient in terms of both hardware overhead and power consumption. FPGAs were initially used to realize large hardware integrated circuit (IC) designs. They offer a more flexible approach similar to that of software, but with the efficiency and performance of a full hardware design, with low overheads. FPGAs are made up of two-dimensional arrays of configurable digital logic blocks and registers. The FPGA interconnect, which connects blocks and registers is also reconfigurable between these blocks. Very High-Speed Integrated Circuit Hardware Description Language (VHDL) and Verilog are hardware description languages and are used to describe and program FPGAs. This allows the re-configuration of the FPGA (flexibility). Designs can be implemented on FPGAs quickly as there is no physical

process. Because of the parallel nature of FPGAs and how they operate they have become a popular choice when realizing neural networks [8], [50], [70], [71]. The reason FPGA platforms are preferred to software approaches is because they offer a low power and parallel infrastructure which is suitable to support large scale neural networks. FPGA's will be discussed in more depth in the next chapter.

## 2.4.3 Neural networks in ICs

A fully customized hardware design e.g. Application specific Integrated Chip (ASIC) provides an ideal scenario for neural networks. It provides a low area and power efficient interconnect with a large throughput. However, as modelling the size of the network scales, the traditional network interconnect struggles to deal with increasing numbers of neurons within the network. This is due to using bus systems for interconnecting PEs. Each neuron is considered to be an individual PE and thus, as the number of neurons increases, the number of PEs connected to the interconnect increases. This also increases latency and slows the throughput. Therefore, an IC design is not fully scalable using traditional digital interconnects because the bottleneck is the hardware interconnect. The topology of connected neurons is especially important in terms of how neurons are connected within a network, increasing complexity as well as increasing latency. This will affect the speed and performance of the full custom IC design. Neuromorphic ASICs have been designed to replicate the low power and area of the brain onto a chip. The Defence Advanced Research Projects Agency (DARPA)-funded program Systems of Neuromorphic Adaptive Plastic Scalable Electronics (SyNAPSE), aims to develop a full-custom hardware design for neural network implementations that scale to biological levels [72].

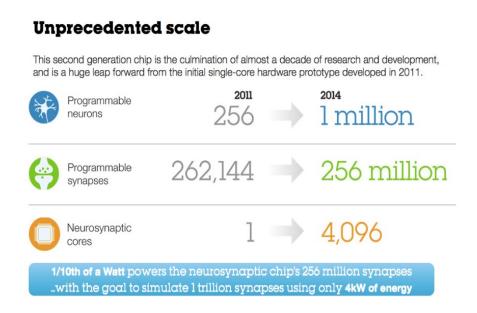

The SyNAPSE program develops TrueNorth neuromorphic chips and attempts to emulate the mammalian brain in electronic hardware. The overall aim is to build a microprocessor system that emulates the mammalian brain in terms of both function and power consumption (10 billion neurons, 100 trillion synapses consuming just one kilowatt [72]). As of 2014 there were 4,096 neurosynaptic chips capable of 1 million programmable neurons and 256 million programmable synapses, consuming just 4 kW of power. This

neurosynaptic chip is considered low power as it differentiates from traditional von Neumann architecture. It operates without a clock and has a low power consumption by optimizing event-driven operations, and therefore, it operates only when it needs to. A number of simulations and applications have been carried out by IBM and Darpa to recreate the efficiency and processing power of the mammalian brain. IBM used a super computer, the Dawn Blue Gene/P with 147,456 CPUs, to create a network similar in size to that of a cats neocortex [73]. Further research was released creating Compass [74] a large scale simulator for cognitive computing a follow up showed the ability to simulate 2.084 billion neurosynaptic cores containing 53 × 1010 neurons and 1.37 × 1014 synapses [75], as well as other applications which demonstrate the use of the neurosynaptic core [76].

TrueNorth [77] was created by IBM and is used on the DARPA SyNAPSE board, there are 16 TrueNorth chips. Each of the chip's 4,096 neurosynaptic cores includes the entire computing package: memory, computation, and communication. Fig.2.8 shows an infographic on TrueNorth released by IBM.

Fig.2.8 IBM infographic on TrueNorth [72].

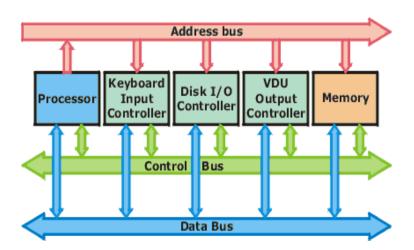

#### 2.4.4 Neural network hardware using on-chip interconnect

Significant progress has been made in synapse and neuron designs, programmability etc. Interconnect scalability remains a challenge which is still not fully addressed. Current approaches to this problem have explored networking concepts such as NoC. NoC technology applies network engineering and techniques for on-chip communication. This has notable improvements over conventional bus and crossbar interconnections. NoC improves the scalability, and the power efficiency of System on Chip (SoC) technologies. The next chapter will provide more insight into such technologies. Using dedicated hardware and digital interconnects, the speed and rate at which neural networks work has been increased. In terms of neuromorphic hardware the key research includes the following:

- Spiking Neural Network Architecture (SpiNNaker) [64] uses 18 ARM9 processors where 16 processors are used for simulating 1,000 neurons each. It uses a NoC packet switched interconnect and two NoC networks, and aims to simulate biological real time, large scale SNN consisting of a billion neurons and trillion synapses. The aim of SpiNNaker is to simulate up to a billion neurons in biological real time.

- Neurogrid [21] is a neuromorphic system (using analogue sensors and a digital interconnect) which simulates a neural system in biological real time. Neurogrid uses 16 neurocores (each neurocore simulates 65,536 analogue neurons) and aims to emulate 1 million neurons in real time with a low power overhead (3 watt) and connects neurocores using a NoC interconnect. Since it only uses 16 neurocores, it can simulate a million neurons and billions of synaptic connections in real time, with a low power consumption. Neurogrid uses software for interactive visualisation and hardware for real time simulation. Neurogrid, however, lacks software flexibility shown by High-Performance Computing (HPC) approaches and due to the limited number of neurons per layer, it is unable to offer biological real time [78].

- FACETS [62] is designed to use an uncut silicon wafer for communication between cores. The wafer consists of many High Input Count Analog Neural Network (HICANN) chips and rather than cut the wafer, a multi-bus NoC interconnect is integrated onto the wafer for communication between chips on the wafer. An FPGA provides wafer to wafer communication, although this limits performance. A single wafer can contain 384 HICANN chips which equates to 196,608 Neurons. FACETS offers hardware acceleration although the trade-off is a high consumption of power.

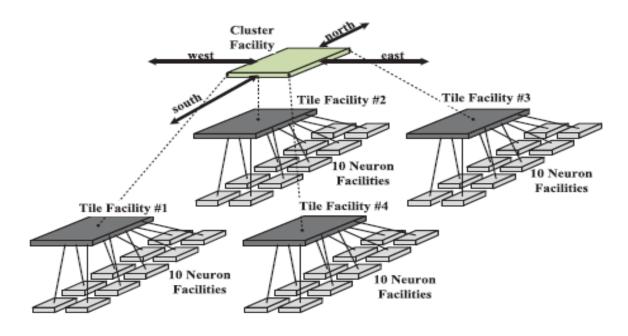

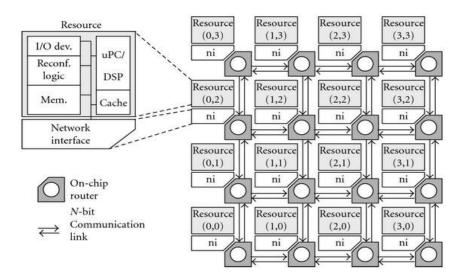

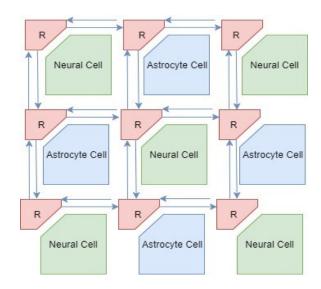

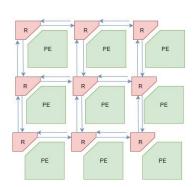

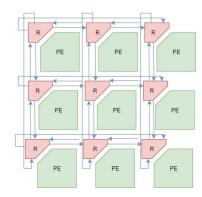

- Emulating Biologically-Inspired Architecture in Hardware (EMBRACE) [8], [63] was developed at Ulster University and uses analogue neurons with a NoC interconnect. EMBRACE offers a Field Programmable SNN solution which is reconfigurable, and due to the NoC architecture, it is also scalable with low power/area consumption. The Hierarchical Networks on Chip (H-NOC) Architecture, is an extension of EMBRACE, and focuses on the structure of the neurons and how the neurons communicate. It uses three communication layers with three separate routers on a single Cluster facility for communication. Fig.2.9 shows an overview of the H-NoC and how neurons are connected with a hierarchical router structure, this enables 400 neurons to interconnect whilst allowing communication on a global scale (many Cluster facilities). H-NoC also offers a spike compression technique [79], which reduces traffic congestion while maintaining biological real time. In addition H-NoC offers hardware acceleration where its NoC throughput performance outperforms that of SpiNNaker, Neurogrid and FACETs [79]. Fig.2.10. shows the H-NoC architecture interacting with an astrocyte network.

- SyNAPSE and TrueNorth [77]. TrueNorth is a neuromorphic CMOS integrated circuit chip. Memory, computation, and communication are handled in each of the 4,096 cores. In essence this is a highly parallel architecture intended to mimic neurons in the brain, however, they are updated serially. TrueNorth consumes 70 milliwatts (0.001% compared to traditional microprocessors) this is because the SyNAPSE chip only draws power for the computation of any calculations.

**Fig.2.9** H-NoC Architecture: This Figure shows the hierarchical approach of H-NoC. The outcome is high throughput or increased spike communication across significant numbers of synapse and neurons [79].

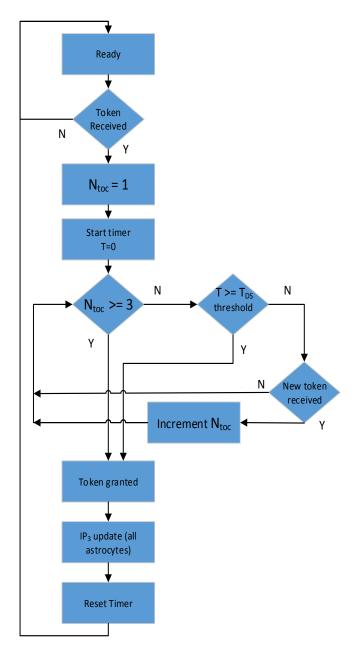

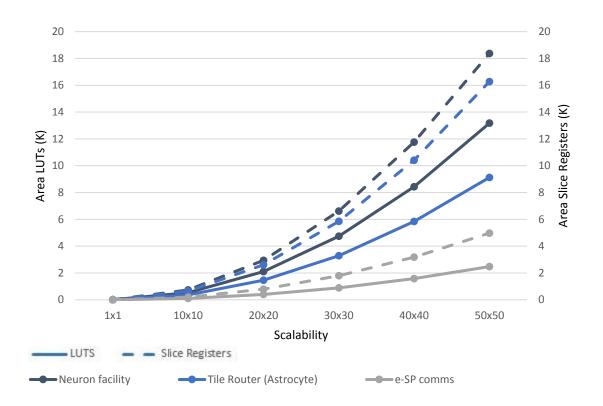

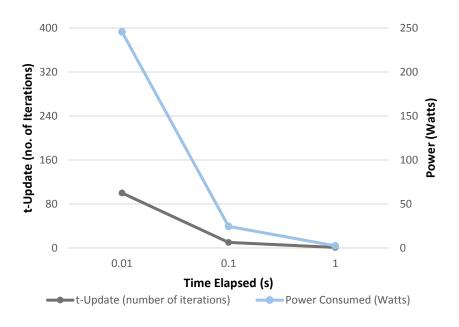

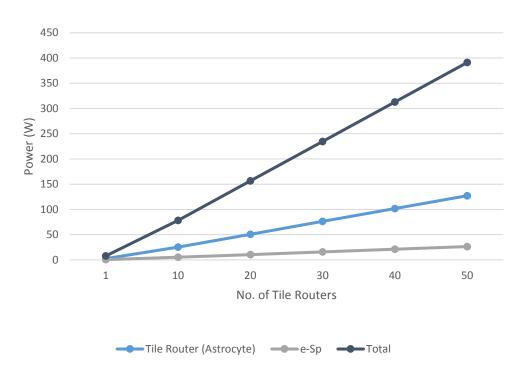

**Fig.2.10** H-NoC/Astrocyte Architecture. This figure shows H-NoC connected to an astrocyte network: This Figure shows the hierarchical approach of H-NoC connecting neurons to astrocytes via the tile router.